本篇文章是我在2021年末碩畢後成為社會新鮮人所參與工作面試的心得分享 "PART 2"

這部分主要會講非一線廠的心得給大家參考,著重在面試 QA 及當時拿到的價碼落點大概是多少~

歡迎大家一起來討論分享,有問題也可以提問喔!!!

嗨嗨~大家好,這邊是九椅特報!

今天就來分享一下我的新人面試 PART 2 啦

內容依序會是

校園徵才活動 -> 義隆、天鈺

104自行投遞 -> 智原、奕力

而 PART 1 的部分主要是介紹 MTK 的面試過程,有需要的夥伴們可以去看看( 我是連結 )

另外,這個系列原本預計會出三篇,但第三篇因為各公司面試內容我覺得重複性很高,

且不是我自己的經驗也不太好撰寫,因此就不打算再出第三篇囉

那就開始進入正題囉~~

校園徵才活動 -> 義隆、天鈺

這是每年3~5月會在北中南區辦的就業博覽會!

2021年南區剛好辦在我學校,當時身為即將畢業(失業)的我,就跟著lab的夥伴們一起去晃晃,

收集一下各公司的資訊也測試一下自己的水準在哪,

當然現場只是填填資料聊聊天,面試都是之後才進行的,

而當時因為疫情的關係,所以很多都是以線上面試的方式進行喔~

首先是第一間 義隆

這間有面到兩個部門缺,新竹數位 IC 部門 及 新竹應用測試部門

先講 "新竹數位 IC 部門" 部分

有先做過大概半小時的小考試,由於是視訊的關係,HR是把題目拍給我,然後我開著視訊作答,作答完再把答案拍照傳回去

再來就進入面試的部分,主要是先介紹自己的研究內容,然後聽主管介紹他們部門負責的部分

部門負責的產品: 主要是 NB 的面板驅動 IC 設計

常用的 tool: VCS、DC、PT、FPGA 等等等的 front end tool

PAY : 6x * 14 + 分紅 (這是 2021 年初拿到的價格喔!!!)

聊完後主管有再做一些QA,我大概被問了6題

1. setup/hold time vio 怎麼解,哪個比較難解

A: setup 最簡單暴力的就是降頻(若 spec 允許的話),不然就是要去看 critical path 中有沒有 cell 可以換成比較快的 cell 來 gen timing

hold 表示資料來得太快嘛,所以就可以在該 path 上墊 buffer 來解,但此時要先看該 path 的 setup time 還有沒有 margin 喔

2. 數位 ic design flow 是什麼

A: 參考這篇就對了, link

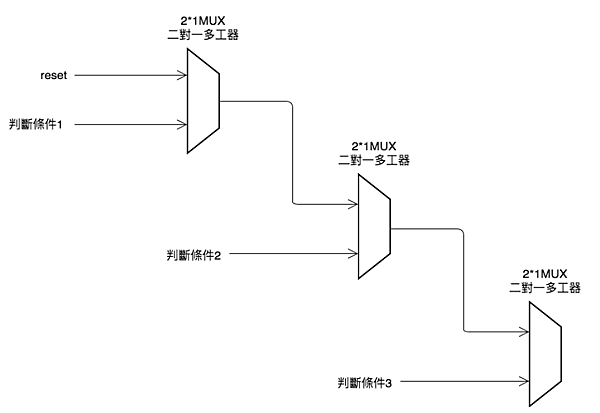

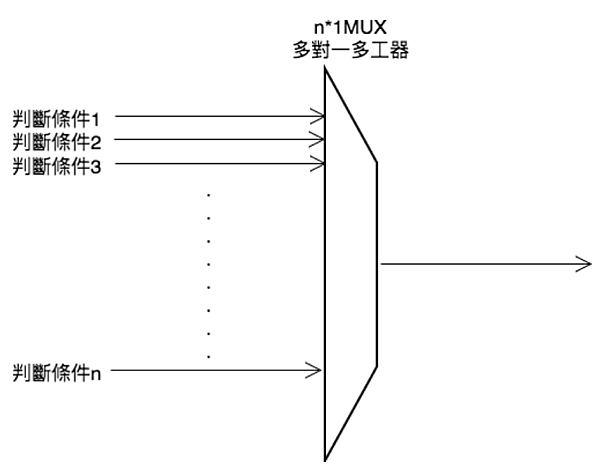

3. if else 跟 case 合成出來的電路差在哪

A: 這個主要就是差在 if else 會有 priority,所以電路會是一級墊一級的

case 就不會有 priority 的現象存在,因為電路大概會是 N對1多工器

4. metastable 解釋一下是什麼,怎麼解

A: 這個在處理非同步 clock 的時候會遇到,但由於碩班接觸到的都是同步訊號,

所以當時答得很模糊,但工作後碰多了就覺得概念清楚多了,之後再出一篇來探討一下 metastable 吧

5. 有什麼最自豪跟最痛苦的事

A: 主要就是在講我自己接計畫做計劃完成計畫的種種過程(訴苦XD)

6. 預計什麼時候畢業 什麼時候可以入職

A: 喔~~當初聽到這個感覺就中了,但由於是人生第一場正職面試,且過程中有聊到 pay 的部分,我覺得算普通,

所以就有先委婉地說再考慮一下

整個過程大概面了 1hr,過一兩個禮拜後有收到二面通知,

但當時我想說要先全力衝口試,因此就先婉拒二面了

再來是 "新竹應用測試部門" 部分

部門負責的產品: TDDI LTDI 顯示觸控整合

常用 TOOL: FPGA 的 ILA,焊接,示波器,建測試環境,不會碰 rtl

PAY: 沒有問XD

這個部門就跟 digital ic design 比較沒有關係,我就不多提了

但因為我自己本身是電類出身,所以面試過程也是很順利XD

第二間 天鈺

這間有面到兩個部門缺,台北數位 IC 部門 及 新竹 TCON 部門

兩個部門的大主管是同一位主管

部門負責的產品:

台北: 主要做 power ctrl 及 edge system 相關的 IP, 另外需要 support 新竹 TCON 部門

新竹: 主要做 TV NB 等等的 display 控制, 影像處理演算法實現, 影像處理 IP 開發

常用的 tool: VCS、DC、PT、FPGA 等等等的 front end tool

PAY: 2021大M新人價 * 14 + 分紅(這是 2021 年初拿到的價格喔!!!)

這間是兩個部門一起面試,一樣有先做過大概半小時的小考試,

再來就進入面試的部分,主要也是先介紹自己的研究內容,然後聽主管介紹他們部門負責的部分

QA的部分就被問得很細,例如:

1. vivado 有下過什麼特別的 constraint

A: 令一個sub module只能用 dsp 來組合,寫法是 verilog 裡面加(*use_dsp48 ="yes"*)

2. axi bus protocol

A: 這個也是個很大的題目,之後再發一篇來探討XD

3. 整個硬體的 design flow 怎麼構思的

A: 先用軟體設計一套 CNN 流程, 再分析其中哪些動作在 CPU 上很花時間,

像 conv pooling padding 在 CPU 處理效率差, 就用專用硬體來支援這些 function,降低 CPU loading

4. simulation 怎麼驗證結果對還錯

A: CPU 用 A 圖跑一次模型會得到結果,這個結果當作 golden

硬體也用一樣的模型跑 A 圖, 得到的結果再去跟 golden 做比對

時間大概面了 2.5hr,過程也都聊得滿開心的,主管講話挺好笑的XD

大概過了一個月後有收到二面通知,二面就是跟大主管聊聊天交換一下想法而已,最後有拿到口頭 offer

這邊要先感謝一下天鈺HR跟面試的主管們,因為我大概是5月就拿到口頭offer,但我一直沒有給肯定的答覆,

他們就一路跟我保持聯繫到我畢業當兵完,但我最後還是選擇去其他間了 抱歉XDDD

104 自行投遞 -> 智原、奕力

由於之前的兩間都是在口試前好一陣子面的,

所以這兩間的面試時間點是我畢業後要開始面 MTK 前排的面試(為了練習XD)

第三間 智原

這間有面到兩個部門缺,新竹 SoC 部門 及 新竹 PCIE 部門

先講 SoC:

部門負責的產品: 公司的 project 與 SoC 相關的都由他們負責

常用的 tool: ncverilog、Vivado、DC、PT 、VCS、PERL、 PYTHON、C

PAY: 2021大M新人價 * 14 + 分紅(這是 2021 年末拿到的價格喔!!!)

一面是視訊面試,主要也是先介紹自己的研究內容,然後聽主管介紹他們部門負責的部分

部門 flow: 開 spec,整合所需 IP 至 SoC,整合後須驗各個 IP 是否能正常 work,也會有 low power design,

部門不用管 APR 部分,但下線後若有問題就要與 APR team co-work,

也要與 SW 部門 co-work 驗下線前後的整個 SoC 及內部各 ip 的 func 是否能 work,

需要設計自動化系統支援快速設計驗證或讓客戶使用更便利,

接著就是QA,主要都在問論文內容跟 AXI 協定的問題,也有說其他專業考試會在二面到現場才進行,

另外有被問說有面過哪些公司,有什麼 offer 了嗎(據實回答就好)

再來就是一週後的二面,也是我人生的第一場實體面試

到公司後有先考半小時的小考跟半小時的英文考卷,題目偏多寫得超趕

再來是先面HR,內容主要也都是聊天而已,HR人很好很好聊XD

最後是面處長,

這邊我是簡介學經歷,論文重點帶過

然後就想辦法推銷自己,說服別人為何要錄取你

再來就開始談 pay 了,當時有提到還有 MTK 要面

他們也願意等我全部面完再給他們回覆

最後的最後,一面的面試官有再進來跟我聊滿多的

強調在他們那工作生活可以很 balance ,CP 值高

學的東西帶得走,以後要跳哪都很好跳

人真的 nice 誠意十足,但我最後還是選擇去其他間了XDDD

PCIE:

部門負責的產品: PCIE IP 設計驗證整合

常用的 tool: VCS、DC、PT、FPGA 等等等的 front end tool

PAY: 沒有談

這部門面試時我已經有心儀的 offer 到手,但想說面試都排了就面一下吧XD

這場也是視訊面試,主要也是先介紹自己的研究內容,然後聽主管介紹他們部門負責的部分

比較特別的是QA採用簡單快速解釋專業術語的方式進行,很像在搶答,沒想法可以直接喊下一題,滿好玩的XDD

然後有再考兩題白板題

1. level 波型轉 pulse 波型

2. 把訊號從 100MHz 轉到 30MHz 的頻率內

第四間 奕力

這間有面到兩個部門缺,TCON 部門 及 ALG 部門

產品: 手機面板驅動(小尺寸面板)、影像處理演算法

常用 TOOL: VCS、DC、PT、FPGA 等等等的 front end tool

PAY: 沒有談

面試是視訊面試,主要也是先介紹自己的研究內容,然後聽主管介紹他們部門負責的部分

再來QA就是一些名詞解釋後直上白板題

1. 劃出一個 2 對 1 的 mux

2. 若只能用一個 2 對 1 的 mux,讓 mux 的輸出為 y=AB,要怎麼做

3. 若只能用一個 2 對 1 的 mux,讓 mux 的輸出為 y=AB,且輸入只能用 A 和 B 不能用 VDD 跟 GND,要怎麼做

---以上三題是連鎖題,很有趣也滿簡單的,可以自行思考一下喔~

4. RTL 寫一個 0 加到 8 的 code

這間一面結束後就...沒有然後....

沒有消息了XDD

最後整理一下重點

1. 在面試想要的公司職缺前,可以先去面其他公司練一下感覺,

主要是要練報告的流暢度及抓一下業界對自己論文會在意的點是什麼

2. 面試結束後可以統整一下這場面試被問的重點,再去看一下自己準備的 slide 需不需要優化

3. 被問的問題都據實回答,不會就說不會,可以順便看看主管的耐心程度XD

千萬不要不懂裝懂亂回答

好啦~ 以上兩期的面試過程及心得就結束囉

下一期預計會出在 MTK 工作一周年心得感想吧

再麻煩大家賞臉給予指教囉!

啊~以上的內容若有錯或有想討論的都歡迎留言唷!

留言列表

留言列表

.png)