本篇文章將分享我對"數位IC設計的流程理解"和"數位IC設計在各階段會用到的EDA Tool及其功能"

主要會focus on Fornt-end,Back-end就放個流程圖供大家參考

我就不獻醜了(不是我負責的部分XD)

歡迎各位一起來交流想法喔~~~

嗨嗨~各位好,這裡是九椅特報!

今天要來介紹數位IC的整個設計流程和各階段會用到的EDA Tool及其功能,

廢話不多上,讓我們直接看圖!

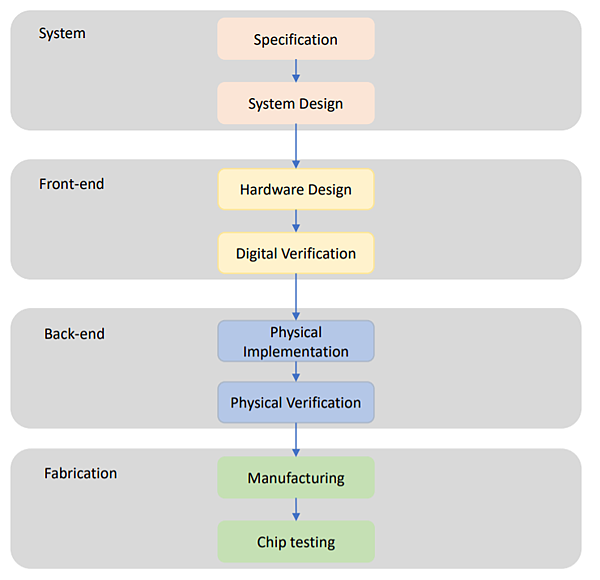

從下圖中我直接把流程拆成4大區塊,"System""Front-end""Back-end""Fabrication"

我先簡介一下這四個區塊~

System: 事先制定規格並利用軟體模擬該規格是否能達到預期效果

Front-end: 將預期的功能利用 RTL 來設計電路

Back-end: 將 Front-end 設計好的電路 mapping 到電路板上

Fabrication: 將經過 Front-end 及 Back-end 的設計圖送到 Fab 廠(TSMC、UMC...)進行晶片生產

以上是我對四個區塊的簡單描述,再來就進入到今天的重點 Front-end digital design!

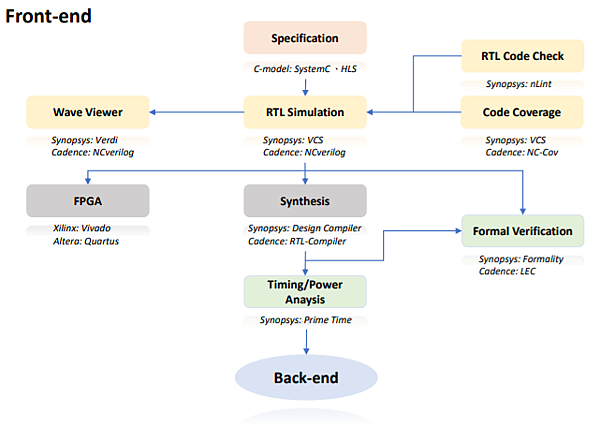

1. Specification

Front-end 的最開始,工程師當然是要直接參與整個開 SPEC. 的決策過程,

部分大公司會有一個專門的部門來根據制定好的 SPEC. 建置 C-model,

藉由 C-model 來模擬整個硬體是否能達到預期的 PPA,

據我所知,大部分都是用 SystemC 來進行硬體模擬,

HLS 則是工程師可以撰寫 C語言來描述所需功能,再合成至 FPGA進行模擬,

但由於 HLS 在"C語言轉譯成 RTL 的效果不太好",因此這個 Tool 還不是很普及!

2. RTL Simulation

再來就是撰寫硬體描述語言(RTL),

目前亞洲及美國普遍都是用 verilog 來進行設計,歐洲則是用 VHDL 比較多,

這邊主要會用到的 EDA tool 有

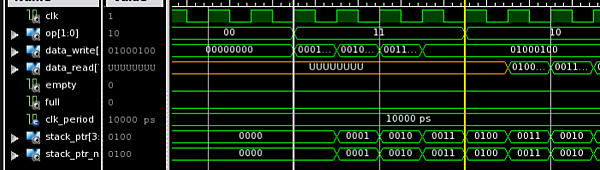

VCS+Verdi、ncverilog:初步檢查 RTL code 是否合乎規則,並進行電路波型模擬

當然,要進行波型模擬就需要撰寫測試集(testbench, tb)

這個 tb 需盡可能包含電路可能會遇到的狀況,

才能知道電路的輸出結果是否能符合功能需求,

此時的 Simulation 可以稱為 pre-RTL sim.

nLint:初步檢查撰寫出的 RTL code 是否能生成出可合成的邏輯電路

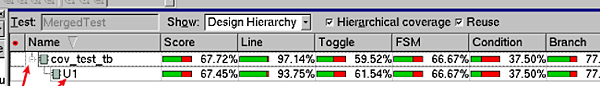

Code coverage:則是藉由 Simulation 結果來判斷 RTL 是否有冗餘的描述

Line:表示每一行 code 是否都有被執行過

Toggle:表示每個 bit 是否都有變化過

FSM:表示狀態機所描述的狀態是否都有執行過

Condition:表示每個判斷條件是否都有被執行到

Branch:表示 if...else if...else, case 的所有分支是否都有發生過

3. FPGA

在學界,考量到下線經費龐大且可能回來的 chip 會 fail,

因此近期滿多學生會直接 import 到 FPGA 看自己的 design 是否能在 FPGA 上跑成功,

但這時候就需要探討到如何跟板子上的 SoC進行溝通整合,需要懂一定的 bus protocol,

也需要去寫 driver 來驅動整個 FPGA,這份工也是非常麻煩的!

而在業界,需要保證 design 驗證的 coverage 夠高,

因此需要跑非常大量的測資來做驗證,

倘若單純用 RTL simulation 跑一億筆測資,可能需要跑個2~3天,

但透過 FPGA 可能只需要1小時即可完成,

且 FPGA 也可以直接做一些實際應用,來確保整個 design 整個 system整合起來是可以 work 的!

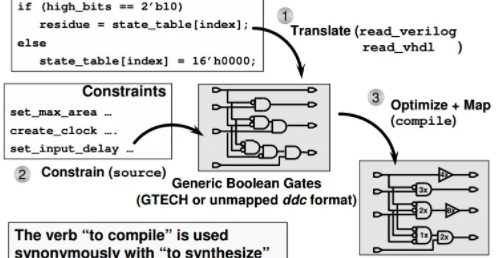

4. Synthesis

接著,會把撰寫好的 RTL 藉由 Design Compiler(DC) 從 Cell library 找到適合的元件來進行電路合成,

而怎麼樣是適合的呢?

這步 Tool 就會根據工程師事前設定好的參數(Constraint) 來決定,

而這些 Constraint 可以決定 Timing, Area, Power 的走向,

例如此次設計一個加法器希望 Area 愈小愈好,不在乎速度,

那 Tool 可能就會選擇使用 Ripple-carry adder 來進行這個加法器的合成(Area小, 速度慢)

又例如這次設計一個加法器希望 Performance 愈高愈好,

那 Tool 可能就會選擇使用 Carry-lookahead adder 來進行這個加法器的合成(Area大, 速度快)

合成結束後,DC 會生成出一串資料集,如:

netlist file:RTL mapping 成邏輯電路的 file

SDC:Synopsys Design Constraint,設計者下的 Constraint 資料集

SDF:Standard Delay File,合成電路的 delay 資訊

再來,為了確保合成出來的 netlist 電路功能與原先設計的 RTL 功能一致(不能保證 DC mapping 一定正確),

因此會進行 Gate-level simulation(又稱 post-RTL sim.),

這邊的作法會將 DC 合成出來的 netlist file 及 Cell library 還有前面所撰寫好的 tb 丟掉 vcs+verdi 或 ncverilog 進行波型模擬,

但此時的 IO port 名稱會被 mapping 成 Cell library 才看得懂的名稱,

因此這邊最好是能讓 tb dump 出一些運算結果的 file,

藉由運算結果來判斷 pre-RTL sim. 及 post-RTL sim. 是否功能一致,

以上是我還在當學生的時候做的麻煩事XD

進業界之後才知道有 Tool 可以幫忙做比對,

這個 EDA Tool 就是 LEC(Logic Equivaience Check)

他會比較兩者的 function 及 register 數量是否相同,

藉此來判斷 Tool 轉譯是否正確,

但還是藉由 Gate-level simulation 看過整個 function toggle 的狀況會比較安全喔!

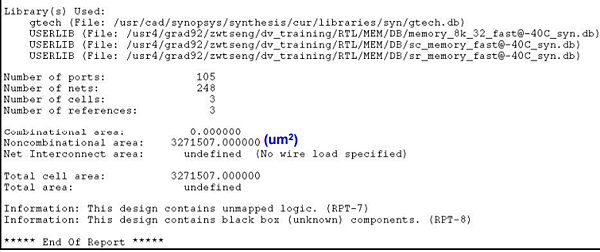

最後,DC 也會可以 dump 出 Area, Timing, Power 等資訊,

這邊 Area 主要可以看 cell area 就好,total area 包含了 wire 的繞線面積,

在還沒跑 Back-end 的情況下看繞線面積很不準!

面積的單位是um2,而這個面積也會跟使用的製程有關,

因此若要跟功能類似但使用不同製程的 design 做比較的話,比 gate count 是最準的!

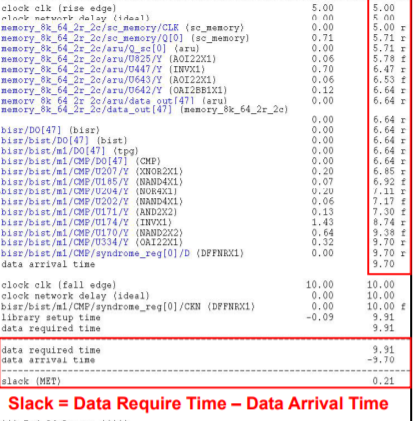

Timing 的部分須注意 slack 不能為負值,

為負值就代表你所設計的電路所需要的最長執行時間(Critical path)超過你所給訂的電路執行時間(period or frequency)

很繞口嗎!? 簡單來說就是你的電路跑太慢了,沒辦法在所設定的時間內完成運算!

這時候可以針對 Critical path 進行調整,

例如:電路的path為

"input" -> "logic1(耗時5ns)" -> "logic2(耗時2ns)" -> "logic3(耗時2ns)" -> output

這時候整個電路的 Critical path 就是卡在 logic1,因為 logic1 耗時 5ns,整個電路的最高頻率就被限制在 200MHz (period 5ns)

倘若能把電路修正為

"input" -> "logic1(耗時3ns)" -> "logic2(耗時3ns)" -> "logic3(耗時3ns)" -> output

這時候三個 logic 是耗時非常平衡的,整個電路的最高頻率也可以來到 333MHz (period 3ns)

但如果整個電路都沒辦法調整的話,那就直接降頻最快啦XD

當然這邊也需要探討到 Setup/hold time 及 CDC 的問題,之後應該會再發一篇文專門探討這個議題!

Power 的部分就不要看 DC 的 report 了,非常不準XD

建議去跑 Prime Time(PT) 看比較準,

PT 這個 Tool 主要可以看 timing 及 power report,

在跑 PT 的時候需要準備波型檔(.vcd 或 .fsdb),

波型檔可以藉由 tb dump 出來,PT 就會根據波型檔所展示出來的狀況來判斷靜/動態功耗,

若 design 有分很多種狀態(IDLE, LOAD, CALCULATION, STORE)

也可以藉由 tb 生成出對應的波型檔,再透過PT來得知各種狀態下的功耗狀況,

這樣可以獲得初步的電路 PPA(Power, Performance, Area) 及 netlist了!

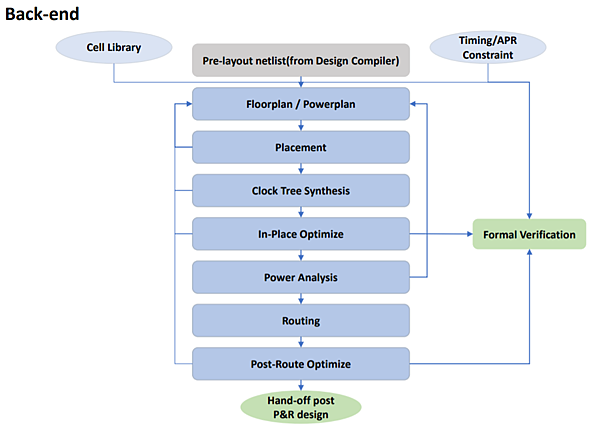

以上大致就是 Front-end 所負責的部分了,再來就把相關資料丟給 Back-end 就完事了XD

當然 Back-end 有遇到什麼問題也很常會來回討論,嚴重的話甚至是需要重新改 design...

因此還是需要了解 Back-end 大致在做什麼(才不會被坑XD)

這邊我畫了一張 Back-end 的流程圖,大家參考參考就好XD

以上是這次關於 Front-end digital design 的介紹,

下期預計會做 "碩班選組 ICS 組分析",

來幫大家分析一下怎麼樣的人適合走 ICS 組,跨到 ICS 組需要具備怎麼樣的能力等等,

就再請大家多多關照啦~~

請先 登入 以發表留言。