嗨嗨~大家好,這裡是九椅特報!

又再度偷懶了好一陣子XDDD

這次就來分享點design小知識好了,這在學校基本上不太可能碰到的項目

Scan chain~

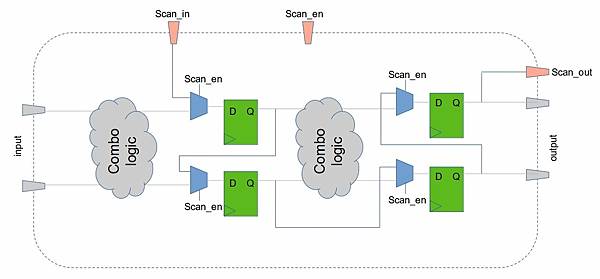

Scan chain的定義是將design中所有的DFF串成一路(下圖藍色線),讓所有的電路都可以被toggle,

並用統一的scan clock去trigger,這樣可以使用預先做好的scan pattern依序送入數bit的方法打進Chip中,

接著開始capture mode,讓各個DFF Q pin去trigger各自對應的combo logic,

而下一級的DFF D pin會收到這組combo logic的運算結果,然後capture mode結束,此時每一級combo logic的運算結果都被記錄了起來,

如此在scan output端就可以獲得一組向量,這組向量再與預先計算好的結果(golden data)做比較,這樣就可以知道Chip是否有錯誤了,也可以推論出錯誤的點在哪一級!

再來呢,

由於Scan的兩大重點是 Controllable & Observable

因此我們會藉由Tmax去看看這個design的scan coverage夠不夠高,

這時候Tmax report就會看到許多不同的Fault,這邊就整理個表格給大家參考

舉兩個比較常見的例子

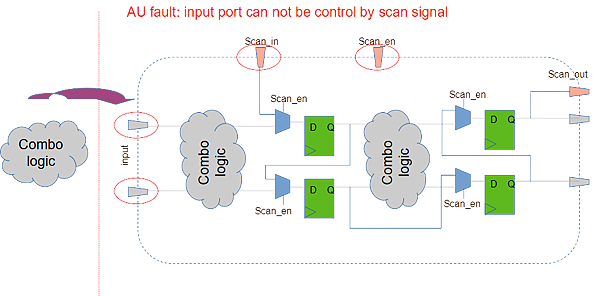

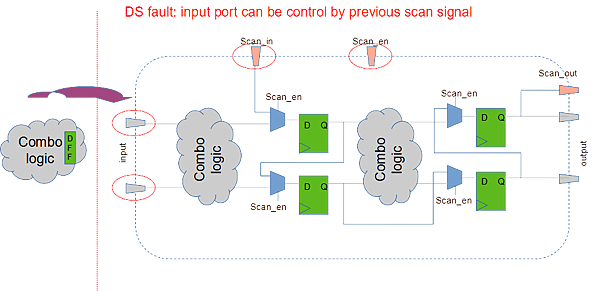

在我們剛剛的圖中Input port並沒有被特別指定說上家的行為是怎麼樣的,

因此就有可能出現兩種狀況: AU or DS

- AU的意思是說,上家的output到我們家的input中間並沒有任何DFF夾在中間,如此就會造成不可測的狀況發生(ATPG untestable)

- DS的意思則是我們已經知道這些input port是可以被測試到的,例如上家的output一定是DFF out或是會灌其他pattern來保證toggle(Detected by simulation)

以上是我對Scan chain的小小見解,

如果在面試過程中有被問Scan相關問題,希望這篇文章內容可以幫助到大家啦!

欸對~

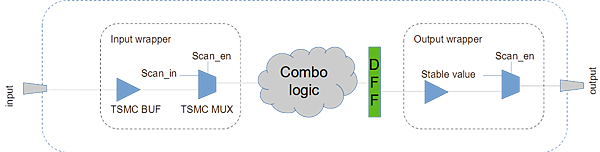

另外這邊再分享一個設計IP時的小技巧,主要分以下四點

- Output必須是DFF out -> 如此是為了把時序切乾淨,盡可能不受上下家干擾

- Input皆要過Scan wrapper -> 讓Scan chain順利串入

- Output皆要過Scan wrapper -> 這邊mux一路選擇Stable value主要是怕有任何不穩定的訊號出現會把下家打掛,因此需要與下家溝通怎麼樣的狀況不會使下家行為異常

- Wrapper cell call TSMC or UMC cell -> 這題就當作一個小題目給大家了,歡迎大家留言分享你的想法囉~

以上就是這篇文章的內容啦!

有問題的話都歡迎提出來討論喔~

善有善報,希望下週開獎給我一個善報>_<

請先 登入 以發表留言。